Product added to cart

Sipeed Tang Nano Minimalist FPGA Development Board

$0.0000

Out of stock

SKU

MIC-05-010

Shop with confidence Learn More

Lattice MXO2-1200 Small System FPGA Development Board Previous

Lattice MXO2-1200 Small System FPGA Development Board Previous

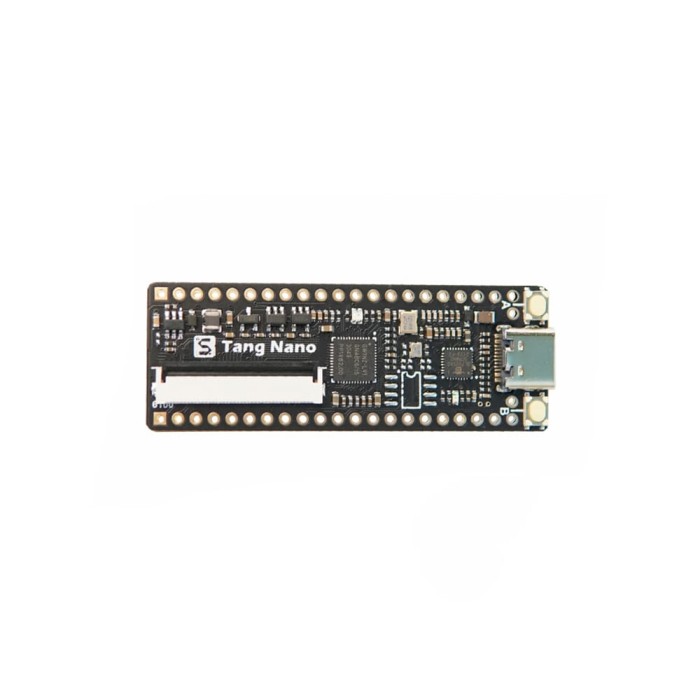

Introducing the Sipeed Tang Nano Minimalist FPGA Development Board - a powerful and versatile platform for FPGA development. Packed with features and functionality, this development board offers an exceptional experience for both beginners and advanced users. With its compact size and minimalist design, it provides a perfect balance between performance and portability.

Equipped with a Xilinx Spartan FPGA, this board delivers impressive processing capabilities and flexibility for a wide range of applications. It boasts a generous 4MB SPI flash for storing your FPGA designs, ensuring ample space for your projects. With 48 GPIO pins and numerous peripheral interfaces, including USB, UART, and I2C, the Tang Nano enables seamless integration with external devices and sensors. Its onboard WiFi and Bluetooth modules further expand its connectivity options for IoT and wireless applications. Whether you're diving into FPGA programming or building complex digital circuits, the Sipeed Tang Nano Minimalist FPGA Development Board empowers you to bring your ideas to life with ease.

Note: Please refer to the board's documentation and resources for comprehensive setup instructions and examples. Ensure proper power and signal connections, and exercise caution when working with FPGA devices to prevent damage to the board or other components.

Specification of Sipeed Tang Nano Minimalist FPGA Development Board:

- The deal: GWIN-1-LV:LUT4: 1152,Flip-Flop: 864,SRAM: 72 kb,Flash: 96 kbp,PLLs+DLS 1+0,Core tension: 1,2 V

- Programming: USB

- Power supply: 5 V - USB C

- Current consumption: up to 400 mA

- Power circuit: each Bank has a separate LDO power circuit (except for BANK0/3). I/O level in BANK 1 and BANK 2 can be adjusted by changing the LDO circuit

- Display: 40-pin FPC - built-in display backlight controller

- I/O: 32-pin

- PSRAM memory: 64 Mb 3.3 V

- LEDs: built-in RGB LEDs

- Button: 2 buttons 3 x 4 mm

- Quartz: built-in 24 MHz quartz oscillator

- Operating temperature: -30°C to 50°C

- Dimensions: 58.34 x 21.29 mm

Write Your Own Review

Please complete your information below to login.

Sign In

Create New Account