Product added to cart

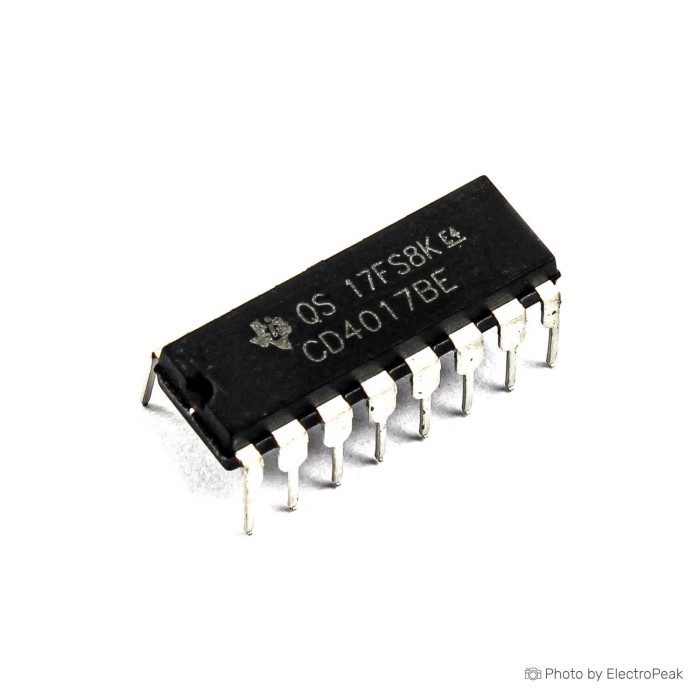

CD4017BE Decade Counter (DIP-16)

$0.3150

In stock

SKU

ELC-01-014

Volume discounts:

- +100 4 % $0.3030

- +500 6 % $0.2970

- +1000 8 % $0.2910

- +5000 10 % $0.2850

- +10000 11 % $0.2790

Ships in 2-3 business days, then:

Free delivery in10-15 days by YunExpress on orders over $35.

Free delivery in5-7 days by DHL on orders over $200.

More shipping info

Shop with confidence Learn More

74HC595 Shift Register Previous

74HC595 Shift Register Previous

Description

CD4017 CD4017BE CMOS Decade Counter with 10 Decoded Outputs DIP16 10 Pack Fully static operation | Medium speed operation 10 MHz (typ.) at VDD = 10 V | Standardized, symmetrical output characteristics | 100% tested for quiescent current at 20 V | 5-V, 10-V, and 15-V parametric ratings CD4017B 5-stage Johnson counters having 10 decoded output. Inputs include a CLOCK, a RESET, and a CLOCK INHIBIT signal. Schmitt trigger action in the CLOCK input circuit provides pulse shaping that allows unlimited clock input pulse rise and fall times.These counters are advanced one count at the positive clock signal transition if the CLOCK INHIBIT signal is low. Counter advancement via the clock line is inhibited when the CLOCK INHIBIT siganl is high. A high RESET signal clears the counter to its zero count. Use of the Johnson counter configuration permits high-speed operation, 2-input decode-gating and spike-free decoded outputs. Anti-lock gating is provided, thus assuring proper counting sequence. The decoded output are normally low and go high only at their respective decoded time slot. Each decoded output remains high for one full clock cycle. A CARRY-OUT signal completes on cycle every 10 clock input cycles in the CD4017B and is used to ripple-clock the succeeding device in a multi-device counting chain.

Features

Fully static operation

Medium speed operation...10 MHz (typ.) at VDD = 10 V

Standardized, symmetrical output characteristics

100% tested for quiescent current at 20 V

5-V, 10-V, and 15-V parametric ratings

Write Your Own Review

Please complete your information below to login.

Sign In

Create New Account